Linux 中断子系统:GIC 中断控制器

GIC 是 ARM 公司给 Cortex-A/R 内核提供的一个中断控制器,类似 Cortex-M 内核(STM32)中的 NVIC。

- GIC:Generic Interrupt Controller,通用中断控制器。

- NVIC:Nested Vectored Interrupt Controller,嵌套中断向量控制器。

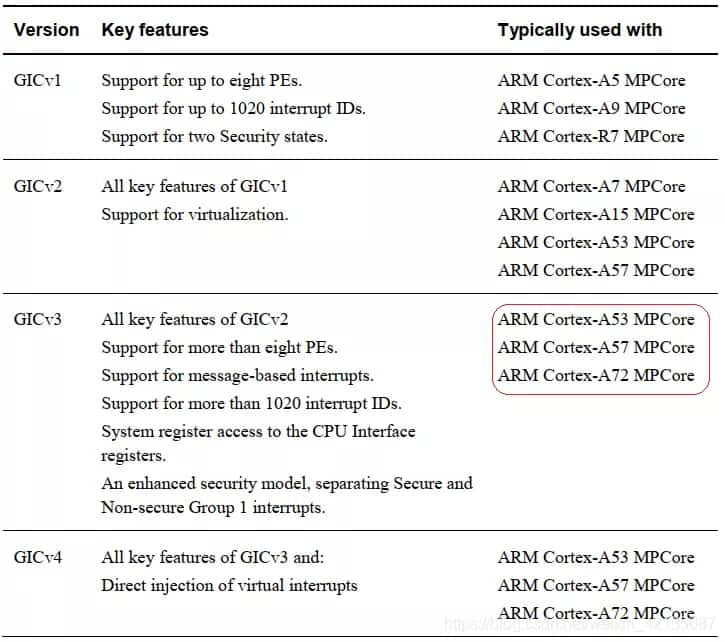

目前 GIC 有 4 个版本:V1~V4,V1 是最老的版本,已经被废弃了。V2~V4 目前正在大量的使用。GIC V2 是给 ARMv7-A 架构使用的,比如 Cortex-A7、Cortex-A9、Cortex-A15 等, V3 和 V4 是给 ARMv8-A/R 架构使用的,也就是 64 位芯片使用的。

我们使用的是 IP 核,也就是 gic400、gic500、gic600。支持对应的架构。

gic400,支持 GIC-v2 架构。

gic500,支持 GIC-v3 架构。

gic600,支持 GIC-v3 和 GIC-v4 架构。

GIC-v2

GIC V2 最多支持 8 个核。ARM 会根据 GIC 版本的不同研发出不同的 IP 核,半导体厂商直接购买对应的 IP 核即可,比如 ARM 针对 GIC V2 就开发出 了 gic400 这个中断控制器 IP 核。

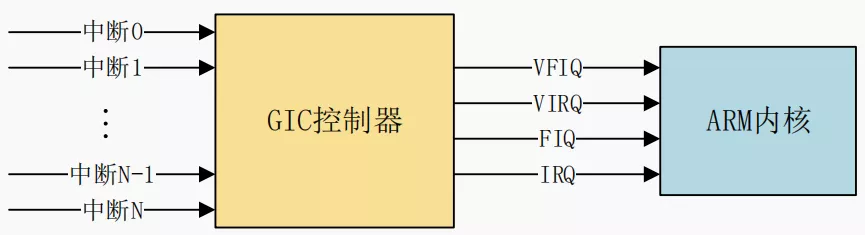

当 GIC 接收到外部中断信号以后就会报给 ARM 内核,但是 ARM 内核只提供了四个信号给 GIC 来汇报中断情况:VFIQ、VIRQ、FIQ 和 IRQ:

VFIQ:虚拟快速 IRQ。

VIRQ:虚拟 IRQ。

FIQ:快速 IRQ。

IRQ::Interrupt ReQuest。

VFIQ 和 VIRQ 是针对虚拟化的,我们不讨论虚拟化中断,剩下的就是 FIQ 和 IRQ 了。一般我们只使用 IRQ,所以相当于 GIC 最终向 ARM 内核就上报一个 IRQ 信号。

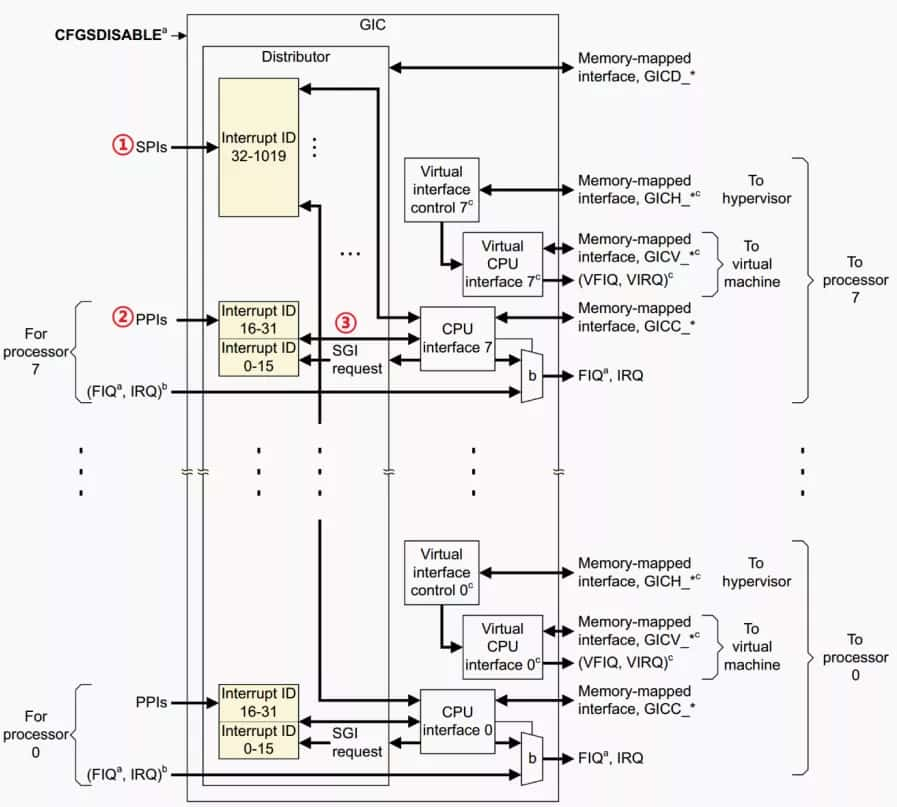

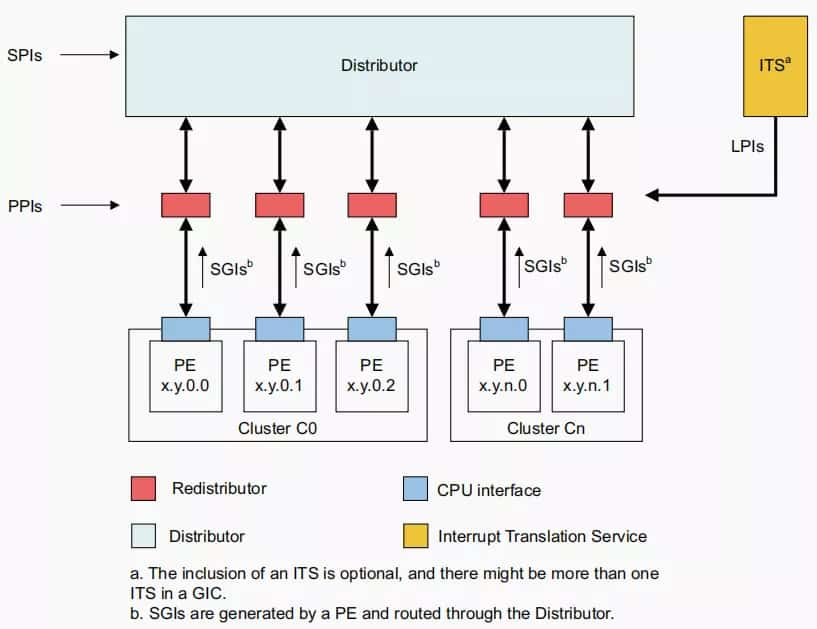

下图来源于ARM官方手册,是 GIC-v2 的框图:

左侧部分就是中断源,中间部分就是 GIC 控制器,最右侧就是中断控制器向 处理器内核发送中断信息。我们重点要看的肯定是中间的 GIC 部分,GIC 将众多的中断源分为 分为三类:

①、SPI(Shared Peripheral Interrupt),共享外设中断,该中断来自于外设,所有 Core 共享的中断。比如按键中断、串口中断等等,这些中断所有的 Core 都可以处理,不限定特定 Core。

②、PPI(Private Peripheral Interrupt),私有外设中断,该终端来自于外设,被特定的核处理。GIC 是支持多核的,每个核有自己独有的中断。

③、SGI(Software-generated Interrupt),软中断,由软件触发引起的中断,通过向寄存器 GICD_SGIR 写入数据来触发,系统会使用 SGI 中断来完成多核之间的通信。

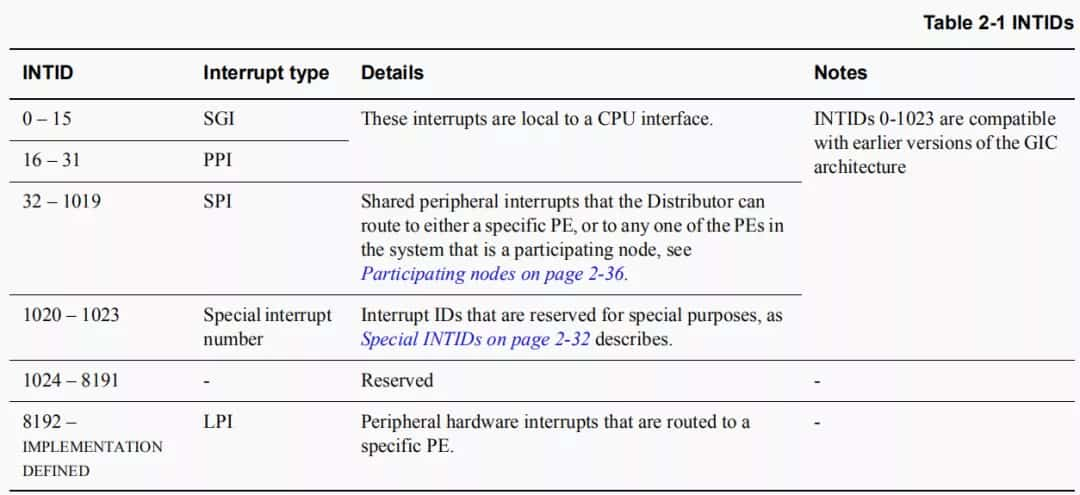

中断源有很多,为了区分这些不同的中断源肯定要给他们分配一个唯一 ID,这些 ID 就是中断 ID。GIC-v2中每一个 CPU 最多支持 1020 个中断 ID,中断 ID 号为 ID0~ID1019。这 1020 个 ID 包 含了 PPI、SPI 和 SGI。这 1020 个 ID 分 配如下:

ID0~ID15:这 16 个 ID 分配给 SGI。每个CPU核都有自己的16个。

ID16~ID31:这 16 个 ID 分配给 PPI。每个CPU核都有自己的16个。

ID32~ID1019:这 988 个 ID 分配给 SPI,像 GPIO 中断、串口中断等这些外部中断 ,至于具体到某个 ID 对应哪个中断那就由半导体厂商根据实际情况去定义了。

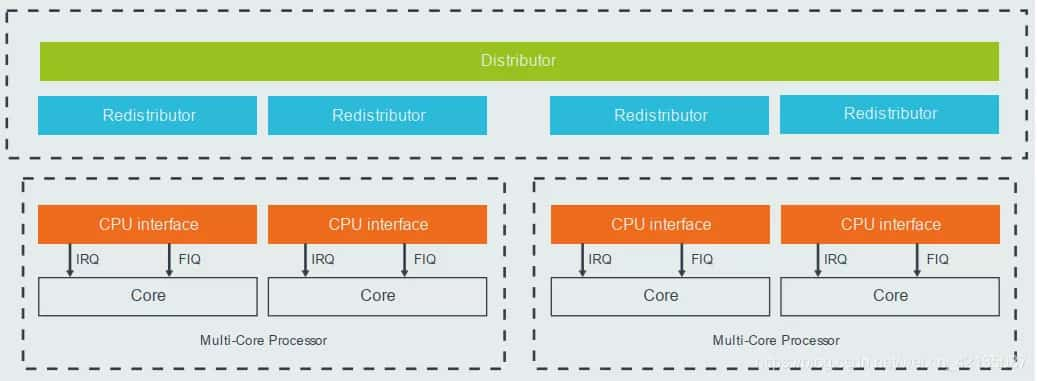

GIC-v2 架构分为了两个逻辑块:Distributor 和 CPU Interface,也就是分发器端和 CPU 接口端。

Distributor(分发器端):中间那个框框,此逻辑块负责处理各个中断事件的分发问题,也就是中断事件应该发送到哪个 CPU Interface 上去。分发器收集所有的中断源,可以控制每个中断的优先级,它总是将优先级最高的中断事件发送到 CPU 接口端。分发器端要做的主要 工作如下:

①、全局中断使能控制。

②、控制每一个中断的使能或者关闭。

③、设置每个中断的优先级。

④、设置每个中断的目标处理器列表。

⑤、设置每个外部中断的触发模式:电平触发或边沿触发。

⑥、设置每个中断属于组 0 还是组 1。

CPU Interface(CPU 接口端):CPU 接口端听名字就知道是和 CPU Core 相连接的,因此在图中每个 CPU Core 都可以在 GIC 中找到一个与之对应的 CPU Interface。CPU 接口端 就是分发器和 CPU Core 之间的桥梁,CPU 接口端主要工作如下:

①、使能或者关闭发送到 CPU Core 的中断请求信号。

②、应答中断。

③、通知中断处理完成。

④、设置优先级掩码,通过掩码来设置哪些中断不需要上报给 CPU Core。

⑤、定义抢占策略。

⑥、当多个中断到来的时候,选择优先级最高的中断通知给 CPU Core。

GIC-v2 支持 bypass 功能,当左上角 CFGSDISABLE 信号为高,外部来的 IRQ 和FIQ 不经过 GIC 仲裁,直连 CPU core 的 IRQ 和 FIQ 引脚。此场景可能用在启动阶段,一般不用。

右上角有 GICD_ 、GICC_ 、GICV_ 、GICH_ 系列寄存器,因为不讨论虚拟中断,所以我们一般只关心 GICD_ 、GICC_ 开头的寄存器, GICD_ 代表 Distributor 分配器的寄存器, GICC_ 代表 CPU interface 的寄存器。

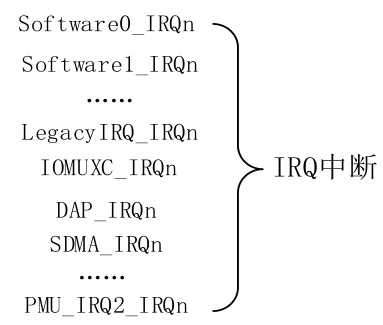

有一点需要说明:不管 GIC 如何对中断进行分类,对 CPU core 来讲,只分为 IRQ、FIQ、VIRQ、VFIQ,一般所有的外部中断对CPU core来讲都属于IRQ:

即便在 GIC 内部分为了 SPI、SGI、PPI,但是最后都会到 CPU interface,CPU interface 再给 CPU core ,CPU core 只认为有四种中断类型,普通都是 IRQ。

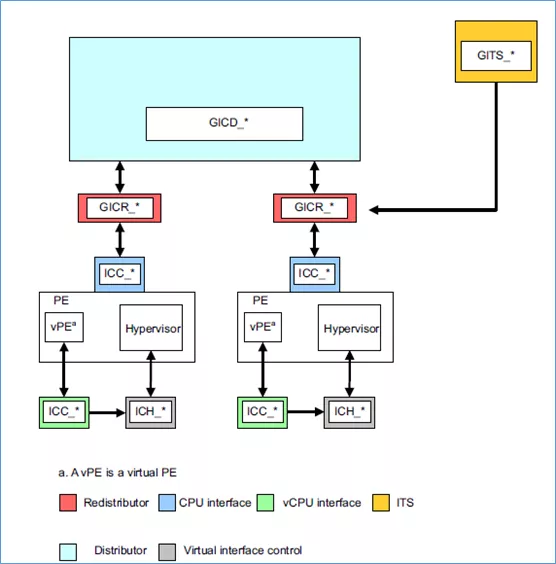

GIC-v3

GIC-v3 架构有改变,中断号也变多了,不过还是向后兼容 GIC-v2 的。

GIC-v3支持超多核,以 xxx.xxx.xxx.xxx 命名,不止8核,GIC-v2 只支持 8 核,命名为 0-7 。

GIC-v3将 CPU interface 从GIC侧移到了CPU侧,因为处理中断会频繁访问 CPU interface 的寄存器,移到 CPU 侧加快访问速度,中断处理就会加快。

GIC-v3 的架构变化如下:以前 SPI、PPI、SGI 都归 Distributor(分发器端) 管,现在只有 SPI 归 Distributor管,PPI、SGI、LPI 都归 Redistributor 管,作用还是一样的。

寄存器分布,不同东西的寄存器开头不一样:

GIC-v 3的中断号规定如下,来源于ARM官方文档。

最主要的区别就是增加了 LPI 这个中断类型,是基于消息的中断。

一般 IRQ 和 FIQ 都会有一个物理线,会给 CPU 核一个物理信号,代表中断到来。LPI 不一样,它是基于消息的机制,写寄存器就会发一个消息中断,是 ARM 在为未来布局,以后会出一些 server 的产品,独享中断号。

GIC-v3 逻辑图总结如下:

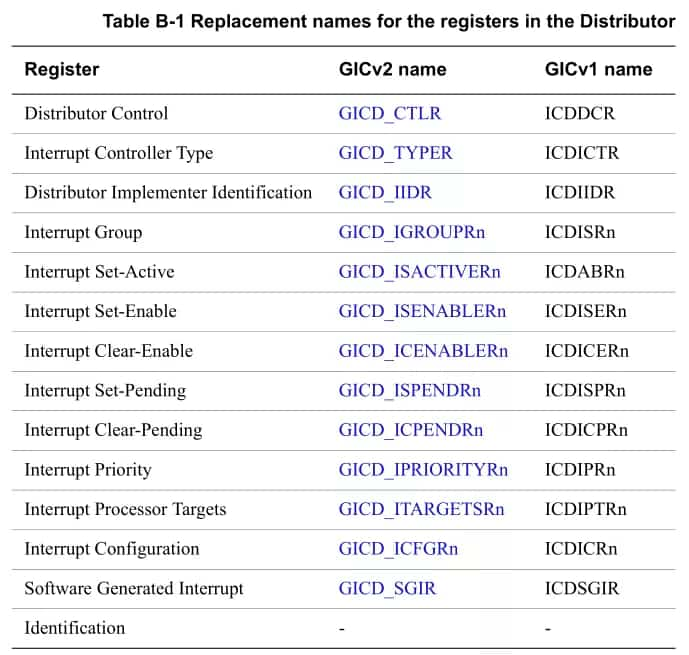

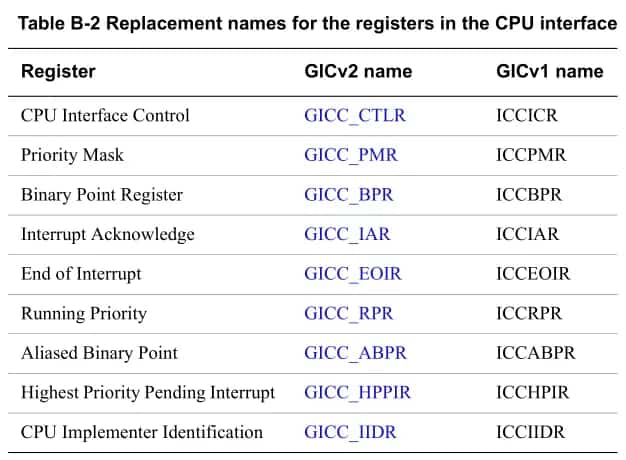

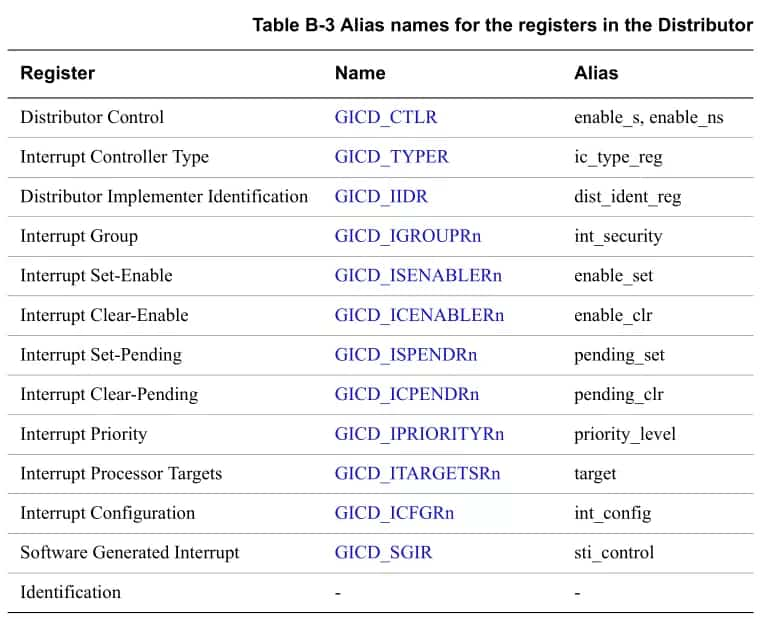

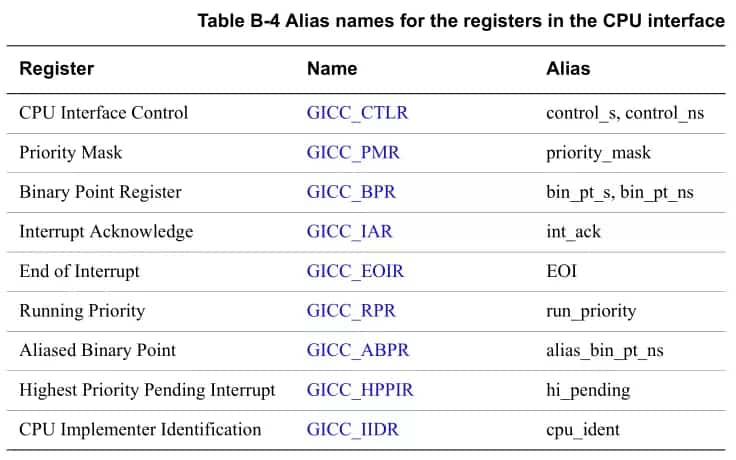

GIC -v2 架构寄存器:

来源于 GIC-v2 手册最后几页:

这里的 alias 别名很有意思,说明了这个寄存器是干嘛的:

GIC -v3的寄存器不一样,是 ICC_ 、ICV_ 、ICH_ 系列寄存器。

页面地址:http://www.youmibao.com/n/538.html

云锁“服务器漏洞修复”功能使用说明

系统漏洞是指应用软件或操作系统软件在逻辑设计上的缺陷或在编写时产生的错误,这个缺陷或错误可以被不法者或者电脑黑客利用,通过植入木马、病毒等方式来攻击或控制整个电脑,从而窃取您电脑中的重要资料和信息,甚至破坏您的系统。“服务器漏洞修复”可以扫描服务器系统,列出未...

服务器安全云锁服务器漏洞修复

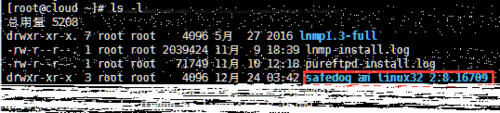

linux服务器安全狗卸载图文教程

当需要卸载linux服务器安全狗软件的时候,首先要用ls命令查看安全狗的文件夹名字,因为我们安装时候的版本不一定相同。一直关注本博客的网友知道,ls-l命令是我们SSH连接VPS时候最经常使用的命令了。ls -l方法/步骤我们能够看到红框里面就是目前使用的安全...

服务器安全狗Linux服务器服务器安全

ubuntu安装vnc启用x11vnc

启动Ubuntu的软件中心,选择“X11VNC服务器”,进行安装。当然也可以用sudo apt-get install命令安装。接下来创建登陆密码复制代码代码如下:sudo x11vnc -storepasswd输入和确认之后,密码被保存到了用户的密码目录下:...

ubuntuVNCx11vnc

总结四条对学习Linux系统有帮助的方法

网络是一个很神奇的东西,现代人的生活离不开网络,网络已深入人们的工作,生活,娱乐等方方面面。网络之所以无处不在,是因为它提供了诸多的网络服务,所以网络服务是网络的灵魂。互联网上的各种网络服务是架构在各种各样的服务器上的。服务器(Server)是提供网络服务的物...

服务器运维linuxlinuxprobelinux学习方法